For the previous 5 years,Intel has lagged behind Taiwan Semiconductor Manufacturing Co. and Samsung in superior chip manufacturing. Now, in an try and regain the lead, the corporate is making a daring—and dangerous—transfer, introducing two novel applied sciences in its desktop and laptop computer Arrow Lake processor, due out in late 2024. Intel hopes to leapfrog its opponents with new transistor know-how and a power-delivery system that will be the primary of its variety.

Over the previous 20 years, Intel has led the sector in making key adjustments to the transistor structure, says Chris Auth, Intel’s vp of know-how growth and director of superior transistor growth. The corporate’s chip manufacturing, nevertheless, has a extra checkered previous: In 2018, Intel couldn’t ship its first 10-nanometer CPU on time, and manufacturing of the chip was postponed a yr, making a scarcity of CPUs made utilizing its 14-nm know-how. In 2020 there have been delays once more, this time for the 7-nm node (rebranded as Intel 4). The corporate has been taking part in catch-up ever since.

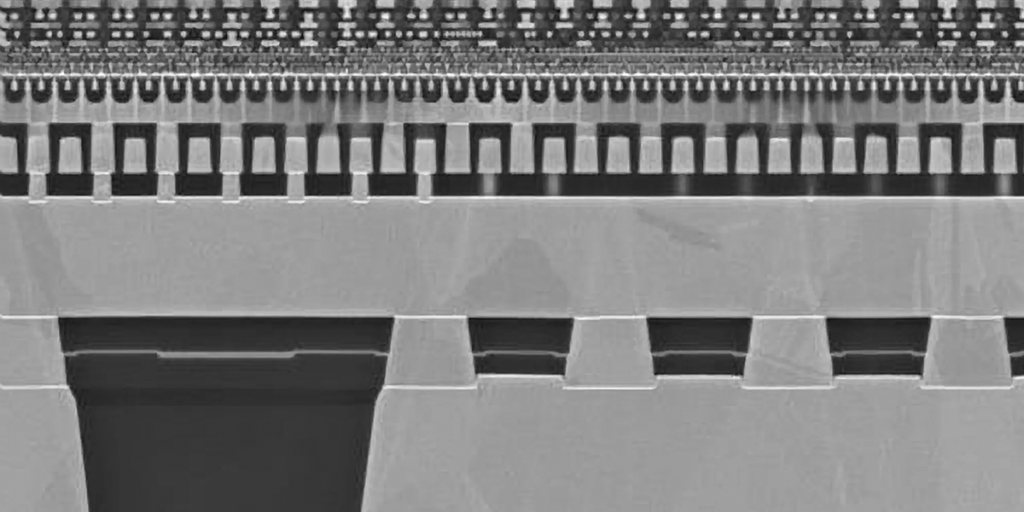

RibbonFET, Intel’s nanosheet transistor, will change right now’s FinFET know-how. FinFET transistors had offered CPUs with low energy necessities and better logic circuit density by wrapping the transistor’s gate round its channel area on three sides as a substitute of only one. However because the FinFETs have scaled down in dimension, these units have approached the restrict of their gates’ capability to regulate present. Nanosheet transistors, equivalent to Samsung’s Multi-Bridge-Channel FET, present higher management as a result of their gates utterly encompass the channel area. Intel expects as much as 15 % enchancment in vitality effectivity with RibbonFET when it’s launched within the upcoming Intel 20A processing node—the corporate’s newest semiconductor manufacturing course of know-how. The “A” in 20A refers back to the angstrom—although, like “nanometer” within the earlier chip-naming conference, it not refers to a selected measurement within the product.

The introduction of a brand new power-delivery scheme—which is mostly referred to as back-side power and which Intel calls PowerVia—is a extra dramatic change. “Ever since Robert Noyce made the primary built-in circuit, all the pieces’s been on the entrance aspect for interconnects,” says Auth. This would be the first time that producers will use the floor on the opposite aspect of the wafer, too, separating energy from processing. That decoupling is essential as a result of energy and sign traces have completely different optimizations: Whereas energy traces carry out finest with low-resistance, high-gauge wires, sign traces want extra space between them to make sure minimal interference.

“It’s type of a brand new playground,” says Julien Ryckaert, vp for logic applied sciences at Imec. The transfer to nanosheet know-how is standard, however Ryckaert expects alternatives for revolutionary new options with back-side energy.

Two Applied sciences at As soon as

Intel determined to introduce each applied sciences concurrently about 5 years in the past, across the similar time it misplaced its lead over opponents. Sometimes, these kinds of initiatives function on a decade-long timeline. As Intel obtained nearer to implementing the brand new transistors and power-delivery community, its executives noticed that these timelines have been set to intersect. So, to get forward of its opponents and keep away from ready for the subsequent node to introduce one or the opposite, the corporate determined to pair the applied sciences. Each are seen as “key linchpins” towards Intel’s formidable purpose to regain the lead in processing technology by 2025, Auth says.

“Intel was once the conservative one,” says Dan Hutcheson, vice chair of TechInsights. Beforehand, TSMC was extra aggressive in its risk-taking, and the corporate extra often missed the mark. Now, the scenario has flipped, Hutcheson explains. “It’s a really dangerous transfer to attempt to implement two main know-how adjustments directly, and previously this has usually been a recipe for catastrophe,” he says.

Intel’s innovation must be delivered with dependable manufacturing to draw and preserve prospects, Hutcheson provides, particularly because it continues to shift its enterprise towards a semiconductor foundry mannequin by separating its manufacturing and product teams. In a foundry mannequin, it’s important that prospects can belief the producer, he says. As a result of long-term funding from growth to delivering a product, prospects are “mainly betting the farm about two years out.”

Firm executives are nicely conscious of the chance they’re taking, given the setbacks and delays Intel confronted with the 10-nm node. Whereas the trade is “constructed on taking dangers,” Auth says, “that was a case the place we took on an excessive amount of threat, and we’re positively cognizant of that mistake.”

So, to cut back the chance concerned within the upcoming 20A node, Intel added an inner node pairing PowerVia with the present era of FinFET. In line with test results introduced in June 2023, including PowerVia alone led to a 6 % efficiency achieve. This inner stepping-stone has allowed the corporate to check out back-side energy supply and deal with any points, each when it comes to course of and design.

On the method aspect, for instance, Intel wants to determine how one can correctly align and hyperlink the back and front sides of the chip with nanometer-size vertical connectors referred to as through-silicon vias which are 1/500 the scale of earlier connectors. One other problem is available in sustaining the flat surfaces wanted to sample the chips when working with each side of the silicon wafer, Auth says.

Given this want for much more precision in manufacturing, it’s value contemplating the projected price, says Mark Horowitz, a professor {of electrical} engineering at Stanford College. Traditionally, price per transistor decreased as producers scaled to higher applied sciences. Now, these price enhancements are typically plateauing. “Transistors will not be getting cheaper as quick as they used to,” Horowitz says.

In the meantime, designers must rethink the interconnect traces and structure. By transferring the facility traces to the again aspect of the chip with PowerVia, Auth says, “you’re undoing about seven years of front-side interconnect studying.” Engineers needed to relearn how one can discover defects and correctly dissipate warmth, for instance. Regardless of the steep studying curve, Intel anticipates important advantages from the mix of the brand new applied sciences.

With every advance addressing an impartial side of scaling, the brand new transistor and power-delivery community could be seen as complementary, in line with Imec’s Ryckaert. He suspects Intel’s resolution to introduce back-side energy through the FinFET-to-nanosheet transition was made to entice prospects, by offering a extra important profit than both advance might ship by itself. There is probably not many future generations that may use nanosheet transistor tech. “Very quickly, we’re going to see the saturation of nanosheet,” Ryckaert predicts.

Intel expects to be prepared for manufacturing 20A within the first half of 2024. TSMC plans to start manufacturing of chips with its N2 nanosheet know-how in early 2025. Manufacturing of N2P chips—a model with back-side energy supply—is predicted to start by 2026. Samsung has already launched nanosheet transistors in its 3-nm node in 2022 however hasn’t formally introduced a timeline for implementing back-side energy.

Hutcheson believes that each one chipmakers are on the identical path towards back-side energy; Intel is simply the primary to take the leap. If the corporate pulls it off, that threat might enable it to regain the lead, he says. “There’s so much driving on this.”

This text seems within the January 2024 print challenge as “Intel Hopes to Leapfrog Its Rivals.”

From Your Website Articles

Associated Articles Across the Net