It’s heady times in power electronics. After a long time of domination by silicon, two newer supplies—silicon carbide and gallium nitride—have begun taking up multibillion-dollar markets. Silicon carbide is now the semiconductor of alternative for the inverters and chargers in electric vehicles, for instance. And should you’ve bought a wall charger recently on your smartphone or laptop computer, likelihood is good that it makes use of gallium nitride.

The newer supplies, often known as wide-bandgap semiconductors, are taking up these and different power-electronics functions as a result of they provide many superior traits. And but wide-bandgap applied sciences nonetheless have basic weaknesses. For a silicon-carbide transistor, an enormous one is comparatively low mobility of electrons within the channel—the realm underneath the system’s gate by way of which present flows between the supply and the drain. That low mobility prevents SiC transistors from switching at excessive charges. That, in flip, limits their effectivity in functions reminiscent of changing between alternating present and direct present. Gallium-nitride transistors, however, have a quirk often known as “dynamic on-resistance,” which signifies that when the system is conducting present, the resistance of the system relies on the voltage—larger voltage means larger on-resistance. One other drawback with GaN is that the bodily dimension of the system, and subsequently its value, goes up as its voltage-blocking functionality does, a key capability for units anticipated to activate and off voltages which might be many instances larger than these discovered inside, say, a typical laptop.

What should you might mix GaN and SiC in a single system that minimizes the weaknesses of every and maximizes their strengths? That’s the query that drove a staff of 16 researchers on the Hong Kong College of Science and Expertise and three different establishments in China. After years of work they lastly claimed success by fabricating a transistor, which they name a Hybrid Subject-Impact Transistor, or HyFET. They described their work in a paper offered on the IEEE International Electron Devices Meeting, held this previous December in San Francisco.

A scanning-electron microscope (SEM) picture of a HyFET, trying down on the system [a], clearly reveals the gate and a supply. A cross-sectional SEM picture of the HyFET [b] reveals the gallium nitride transistor on the prime and the silicon carbide beneath. Different SEM photos present the gate area of the GaN system [c], and the channel of the SiC transistor [d and e]. The Hong Kong College of Science and Expertise

Consultants in wide-bandgap semiconductors not concerned with the analysis had been impressed with the technical achievement. “I truly am very excited in regards to the outcomes of Kevin Chen’s group in Hong Kong,” mentioned IEEE Fellow Debdeep Jena, a professor and laboratory chief at Cornell University. “It has numerous advantage and promise.” Nonetheless, these specialists’ opinions in regards to the system’s industrial prospects had been usually extra circumspect.

In operation, the system makes use of a low-voltage, excessive pace GaN transistor to manage a high-voltage SiC junction field-effect transistor (JFET). In a traditional SiC JFET, the drain is on the backside of the system, linked to the substrate. Present flows vertically, managed by a gate on prime of the system, by way of a “drift layer” to a number of supply terminals, additionally on prime of the system. Within the Hybrid FET, that primary configuration is recognizable: there’s a drain on the backside of the system, linked to the substrate. Present flows upward by way of a SiC drift layer. Nonetheless, the gate and supply terminals are in a GaN transistor built-in instantly above the SiC JFET, on the prime of the system. So the present flowing by way of the SiC JFET is managed by a gate and supply terminals which might be within the GaN a part of the system.

The benefit right here is that it’s the GaN transistor, with its excessive electron mobility, that controls the switching of the mixed system. And constructed on the muse of the SiC JFET, with its massive drift area, the mixed system has the voltage-blocking capabilities of SiC. Testing indicated that the system largely fulfilled the researchers’ expectations. Though the mobility is just not fairly as excessive as for a traditional GaN system, it’s “appropriate for high-frequency switching,” they discovered. Additionally they demonstrated that within the “off” state the system might block round 600 volts, relying on temperature—not dangerous for a first-of-its-kind experimental system.

Many challenges needed to be surmounted to manufacture the system. One of many main ones was rising a GaN transistor instantly on prime of an SiC one. Gallium nitride units are routinely fabricated on substrates of SiC. Nonetheless, these units are grown “on axis,” which means they’re grown layer by layer with every layer parallel to the substrate. However SiC units are sometimes grown off axis with respect to the orientation of their substrate crystal’s lattice. So the researchers needed to devise a method of rising a GaN transistor on prime of an SiC system with a deviance from the axis, or “miscut,” of 4 levels.

To do that they developed a method that they name “two-step biaxial pressure launch.” A basic drawback with the interfaces between two completely different semiconductors is the pressure created on the boundary the place the 2 dissimilar crystals merge. This pressure can create performance-robbing imperfections within the lattice known as dislocations. The approach refined and exploited by the researchers releases the pressure by way of two particular sorts of dislocations, minimizing its detrimental results.

One of many weaknesses of the Hybrid FET is its resistance to present move when the transistor is within the on state. This worth, known as Ron, is kind of excessive, at round 50 megaohms per cm2. Greater Ron means decrease total effectivity. In fact, the Hybrid FET is actually the primary of its sort, in-built a college laboratory.

“The massive Ron in our paper outcomes from a small system … and a really conservative design within the SiC portion,” wrote creator, and IEEE Fellow, Kevin Chen in an e-mail. “Normally, there are not any further obstacles towards the conclusion of three mΩ∙cm2 (~2.6) for a 1200-V HyFET with industrial SiC manufacturing amenities.”

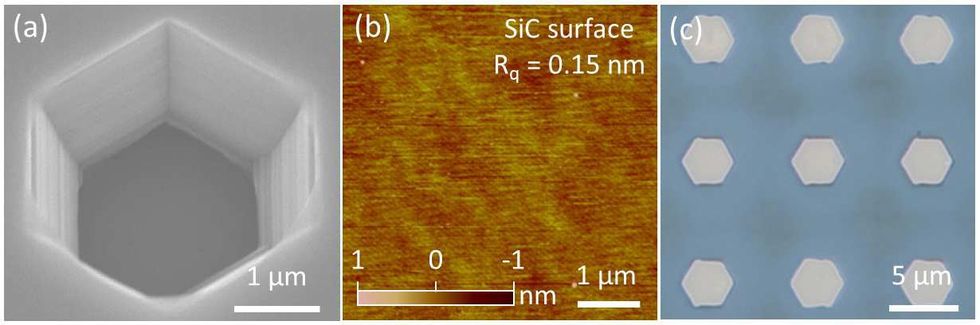

Scanning electron photos present a gap, or through, within the gallium nitride portion of the system [a]. When full of metallic [c], these vias turn out to be conductive pathways enabling present to move between the gallium-nitride and silicon-carbide parts of the system. A picture made with atomic pressure microscopy [b] reveals the floor of a silicon-carbide layer.The Hong Kong College of Science and Expertise

Scanning electron photos present a gap, or through, within the gallium nitride portion of the system [a]. When full of metallic [c], these vias turn out to be conductive pathways enabling present to move between the gallium-nitride and silicon-carbide parts of the system. A picture made with atomic pressure microscopy [b] reveals the floor of a silicon-carbide layer.The Hong Kong College of Science and Expertise

For comparability, although, a state-of-the artwork SiC or GaN transistor able to blocking greater than 600 volts can have Ron as little as 2 mΩ∙cm2, notes IEEE Life Fellow B. Jayant Baliga, the inventor of the Insulated-Gate Bipolar Transistor and a Distinguished College Professor of Electrical Engineering at North Carolina State University. Given these figures, Baliga questions how a lot demand there could be for a industrial Hybrid FET, when a lot easier and, in all probability, cheaper SiC transistors had been out there. “What would encourage somebody to shift to one thing far more sophisticated, with all these layers being grown, if the particular on-resistance is just not lowered beneath that of the silicon-carbide MOSFET?” (Steel Oxide Semiconductor FET), Baliga requested.

IEEE Fellow Umesh Mishra, Dean of the Faculty of Engineering on the University of California Santa Barbara, and a pioneer in GaN energy units, questioned whether or not the benefits of integrating two completely different semiconductors right into a single system—minuscule inductive delays and capacitive losses—had been well worth the prices in manufacturing complexity and different components. To fabricate such a tool, an organization “now has to have two applied sciences that they’re working within the fab,” he notes. “They need to have silicon-carbide expertise, they usually need to have gallium-nitride expertise. No person needs to do this since you now have two sophisticated applied sciences that you’re concurrently attempting to run”—a expensive proposition.

“To scale one thing tough is at all times arduous,” Mishra provides. “Then the query is, what’s your profit?” Mishra notes that almost all of the benefits of the mixed system may very well be obtained at a lot decrease value by merely connecting the 2 completely different transistors collectively in a single package deal, relatively than integrating them right into a single hybrid system.

Creator Chen, nonetheless, steered that undesirable digital traits, significantly a weak point known as parasitic inductance, would plague transistors which might be merely packaged collectively relatively than built-in. “Decrease parasitic inductance minimizes switching oscillation and reduces switching loss,” he wrote in his e-mail. “Superior co-packaging methods might cut back the parasitic inductance to a sure diploma, however will not be as value efficient because the built-in system (realized in a batch course of).”

Jena, at Cornell, famous {that a} doubtlessly insurmountable impediment for the Hybrid FET is the speed of development of GaN units, particularly. Within the foreseeable future, he says, GaN will turn out to be so succesful that it in all probability gained’t require hybrid schemes to triumph. “The physics tells me that GaN is the winner in the long term,” he says. “I don’t wish to take something away from the [Hybrid FET] paper. It’s a terrific paper. However no matter they’ve proven right here may even be attainable with gallium nitride sooner or later,” he concludes.